Calibre Physical Verification

Overview

Calibre physical verification is the industry leader for accuracy, reliability, and performance. The Calibre nmPlatform provides a comprehensive and innovative suite of functionality that enables foundries, IDMs, and fabless companies to efficiently address all physical verification requirements.

The Calibre nmDRC tool has long led the industry, but today’s designs also demand novel technologies that enable design companies to accelerate time to market and achieve faster innovation. From equation-based DRC to multi-patterning, machine learning, and EDA in the cloud, the Calibre toolsuite provides the proven performance, technology, accuracy, and capacity to handle any design, at any node, at any foundry.

Physical Verification

Calibre nmDRC and Calibre nmLVS are the market share leaders in physical verification. Calibre also leads the market with innovative features such as incremental DRC, which ensures you can complete your design rule checking quickly and efficiently, and equation-based design rules, which let designers define continuous, three-dimensional functions that accurately and precisely reflect the complex physical interactions of today’s nanometer designs.

Calibre nmDRC

The Calibre nmDRC platform enables reduced cycle time with revolutionary new capabilities that substantially differentiate Calibre nmDRC design rule checking from traditional DRC tools.

Calibre Auto-Waivers

Calibre Auto-Waivers technology lets users waive false physical and circuit verification violations to focus on real errors, speed design process, make debug more efficient, and shorten schedules.

Interested in Calibre Design Solutions?

Contact us to Learn More

Software for IC Verification

QuestaSim

Simulation and Debug

Combines high performance and capacity simulation with unified advanced debug and functional coverage for the most complete native support of Verilog, SystemVerilog, VHDL, …

Catapult HLS

HLS and Verification

Industry leading C++ / SystemC High-Level Synthesis with Low-Power estimation / optimization. Design checking, code, and functional coverage verification plus formal make HLS more than ….

Questa Inspect

Static RTL Bug Hunting

A fully-automatic formal bug hunting app that finds deeply hidden bugs due to common RTL coding errors, Inspect makes it possible to eliminate a wide range of bugs without a testbench.

Questa CDC

CDC Verification

Questa CDC finds errors using structural analysis to detect clock-domains, synchronisers, and low power structures via the UPF. It then generates assertions and metastability models for …

Questa Lint

Static RTL Verification

Questa Lint provides adaptive, integrated insight to the designer to ensure that the quality requirements and intent are met. Pre-configured methodologies provide immediate, intuitive feedback …

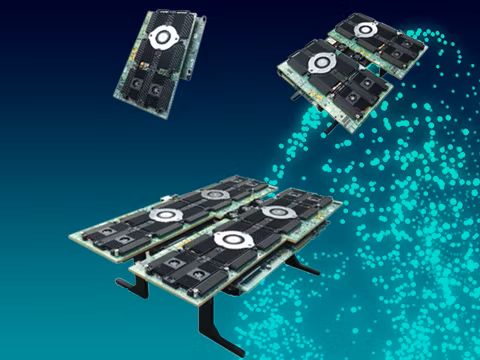

Veloce proFPGA

Hardware-Assisted Verification

The Veloce proFPGA system architecture offers best-in-class modularity, scalability, flexibility and portability to serve the verification requirements of today’s hardware and software engineers.