FPGA & ASIC Design

Is your FPGA design flow ready for the new class of designs targeting the latest complex FPGAs? Are you struggling with point tools that don’t work together? Are you able to meet your QoR goals in the desired budget? Can your PCB and FPGA teams collaborate to achieve the overall system constraints?

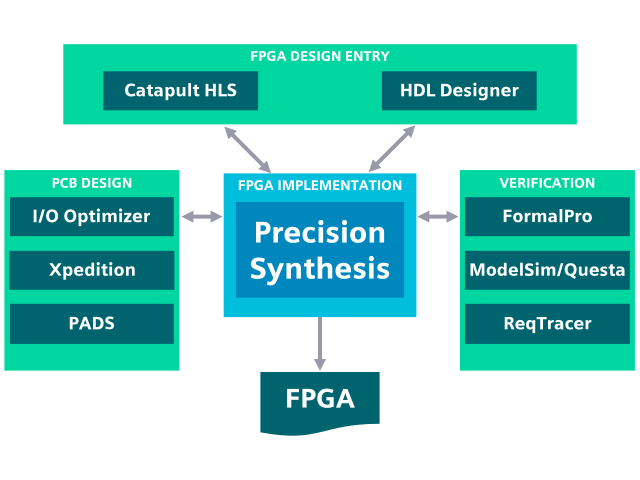

SIEMENS EDA’S COMPLETE FPGA DESIGN FLOW

Siemens EDA’s FPGA design solutions deliver an integrated FPGA design entry, synthesis, verification, equivalence checking, and PCB design platform that speeds up FPGA designs from creation to board, meeting design QoR goals and system constraint requirements.

DESIGN CREATION AND REUSE

Whether designing an FPGA or ASIC, the devices have advanced capabilities and complex features that, when put under tight development cycles, burden the design teams to produce efficient and robust chips. Hence, the design teams have placed more demands on HDL processes, automation, and style guidelines for developing quality design results.

Standard languages (such as VHDL, Verilog, SystemVerilog) and IP formats, along with common industry version management systems aid in producing repeatable and dependable design processes, but the tools that utilise these standards need to do much more than edit text files. Mentor Graphics delivers a complete design solution for FPGA and ASIC HDL development beginning with comprehensive design creation addressing new code creation, formal and informal design reuse, and any combination in between. These HDL design capabilities greatly assist engineers, individuals and teams, in creating, analysing, and managing their complex designs, improving their productivity and accelerating design creation.

Effective design reuse is a critical objective for every electronic design company as 75% of future productivity gains will come through reuse. Executives, managers, and engineers all have a big stake in reuse, but nearly everyone underestimates the challenges associated with it.

HDL Designer

With deep analysis capabilities, advanced creation editors, and complete project and flow management, HDL Designer delivers a powerful HDL design environment.

SIMULATION & VERIFICATION

FPGA devices have gone through radical changes in the last decade, becoming so complex they now resemble complete systems. As a result, they require advanced verification technology to improve FPGA debugging, deliver code coverage, and enhance verification throughput.

This change in FPGA capabilities has resulted in the emergence of advanced FPGA solutions, which include the integration of third-party IP, DSPs, and multiple processors, all connected through advanced high-speed bus protocols.

Mentor Graphics delivers the FPGA verification tools and expertise you need to get high-quality products out the door faster.

ModelSim

The combination of industry-leading, native SKS performance with the best integrated debug and analysis environment makes ModelSim the simulator of choice for both ASIC and FPGA design.

QuestaSim

Combines high performance, high capacity simulation with unified debug and functional coverage for complete native support of Verilog, SystemVerilog, VHDL, SystemC, SVA, UPF and UVM.

FPGA / ASIC SYNTHESIS

With increasing competitive pressures and shorter product life cycles, designers have less time to develop high performance and complex ASIC designs.

At the same time, the development cost of an ASIC is increasing rapidly, making it less feasible to use ASIC devices for many cost-sensitive applications without extensive testing and simulation. As FPGA devices have become larger and faster, verifying functionality of costly ASIC designs in FPGAs has become an effective and economical method of verification. However, some ASIC structures cannot be directly implemented in an FPGA efficiently. Precision Synthesis helps ease the transition from ASIC to FPGA design by allowing the same HDL code and constraint syntax to be used. To obtain optimal performance, automatic conversions of ASIC design structures are utilised.

Precision Synthesis offers high quality of results, industry-unique features, and integration across Mentor Graphics’ FPGA Flow – the industry’s most comprehensive FPGA vendor independent solution.

Precision Series

Precision offers vendor-independent FPGA synthesis. It provides best-in-class performance and area, high-reliability design capabilities and tight links to simulation and formal equivalency checking.

LeonardoSpectrum

LeonardoSpectrum offers customers a well-proven, mature synthesis solution for both FPGAs and ASICs.

HIGH-LEVEL SYNTHESIS & VERIFICATION

Worried your next RTL project will be late? Will your new “secret sauce” design suffice or will it consume too much power? How will you verify it’s functionally correct and optimally crafted before committing to RTL? Catapult High-Level Synthesis (HLS) & High-Level Verification (HLV) changes the game.

The Catapult High-Level Synthesis platform empowers designers to use industry-standard C++ and / or SystemC to describe functional intent, enabling them to move up to a more productive abstraction level for both design and verification of ASICs and FPGAs.

For designs and IP where time-to-market is critical, power / performance information is needed early and specifications are frequently changing (automotive vision, image processing, deep learning, video CODEC, 5G/IoT communications, etc…), Catapult HLS provides the only effective way to meet these pressures without compromising quality and functionality.

Catapult

Industry leading C++ / SystemC High-Level Synthesis with Low-Power estimation / optimization. Design checking, code, and functional coverage verification plus formal make HLS more than just “C-to-RTL”.

REQUIREMENTS TRACING

Clearly tracking hardware implementation for specified requirement validation has become a preferred development practice that is well suited for safety critical projects in medical, transportation, aerospace and military, but is equally significant for any complex ASIC or FPGA design.

The ability to completely trace and manage design requirements from specification through implementation is simply “good project management”. ReqTracer facilitates the deployment of a requirements management process while allowing the project teams to focus on their implementation and verification work for maximum efficiency.

ReqTracer

Simplifies, automates, and enables requirements traceability from specification of the hardware specification through HDL coding, implementation, and validation.

Software for FPGA & ASIC Design

HDL Designer

Visualising RTL Design

With deep analysis capabilities, advanced creation editors, and complete project and flow management, HDL Designer delivers a powerful HDL design environment.

QuestaSim

Simulation and Debug

Combines high performance and capacity simulation with unified advanced debug and functional coverage for the most complete native support of Verilog, SystemVerilog, VHDL, …

Precision

FPGA Synthesis

Provides FPGA vendor-independent logic synthesis, offering reduced time to market, fewer design defects, and superior quality of results. The powerful optimisation engines, context sensitive GUI, …

ModelSim

HDL Simulation

ModelSim’s award winning Single Kernel Simulator (SKS) technology enables transparent mixing of VHDL and Verilog in one design.

ReqTracer

Requirements Management

Simplifies, automates, and enables requirements traceability from specification of the hardware specification through HDL coding, implementation, and validation.

Catapult HLS

HLS & Verification

Industry leading C++ / SystemC High-Level Synthesis with Low-Power estimation / optimization. Design checking, code, and functional coverage verification plus formal make HLS more than ….