Precision Synthesis

Overview

Precision offers vendor-independent FPGA synthesis. It provides best-in-class performance and area, high-reliability design capabilities and tight links to simulation and formal equivalency checking. The powerful optimisation engines, context sensitive GUI, and advanced timing algorithms result in faster designs with higher device utilisations.

Precision Synthesis is the industry’s most comprehensive FPGA vendor-independent solution. It offers best-in-class results for performance and area. Precision has tight integration across the Siemens FPGA flow from C++ / SystemC / RTL design through simulation and formal verification to board design.

Introducing the Precision Series

Precision Synthesis solutions provide high-quality Verilog / VHDL / SystemVerilog synthesis for the latest FPGAs, easy-to-use debug and validation environment, comprehensive & user-friendly high-reliability synthesis, and tight integration with Siemens FPGA design solutions.

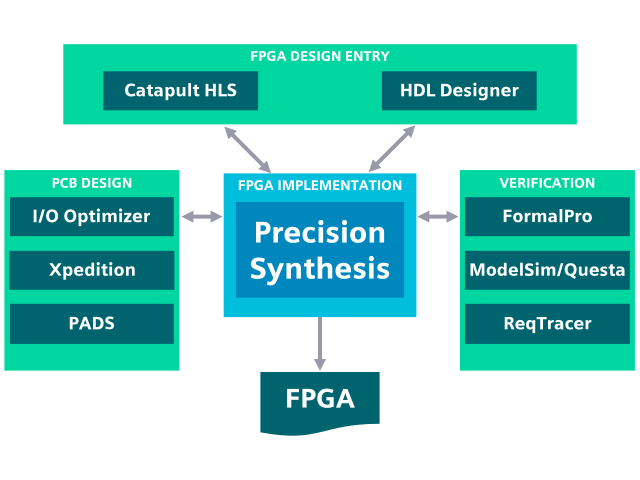

Complete FPGA Design Flow

Siemens EDA’s FPGA design solutions deliver an integrated FPGA design entry, synthesis, verification, equivalence checking, and PCB design platform that speeds up FPGA designs from creation to board, meeting design QoR goals and system constraint requirements, with Precision Synthesis at its core.

The Precision product range includes Precision RTL, Precision RTL Plus, and Precision Hi-Rel covering the complete range of synthesis requirements from small FPGA design through to the largest Vertex and Stratix devices.

Precision RTL

Entry-level FPGA synthesis solution, offers an excellent quality of results, industry – leading Verilog / VHDL / SystemVerilog language support and an FPGA vendor – independent solution.

Precision RTL Plus

Flagship FPGA synthesis and validation solution, offer a best-in-class quality of results, breakthrough advantages for commercial and mil – aero applications.

Precision Hi-Rel

Ground-breaking FPGA synthesis solution, offers a comprehensive & user-friendly environment for mitigation of SEUs / SETs in safety-critical & high-reliability applications.

Key Features and Benefits

- High-performance, easy-to-use, vendor-independent RTL synthesis solution

- Supports VHDL, Verilog, SystemVerilog and EDIF language input

- Powerful RTL and technology schematic viewers

- Advanced retiming algorithm to improve performance

- Interactive static-timing analysis quickly performs “what-if” timing analysis scenarios

- Gated clock conversion and DesignWare support for ASIC prototyping

- Support for industry standards with SystemVerilog and Synopsys Design Constraints (SDC) format

- Design Bar guides users step by step through synthesis, analysis, placement and routing

- Optional Register Retiming algorithm moves registers across logic to improve performance

Interested in Precision Synthesis?

Contact us to Learn More

Tools for FPGA & ASIC Design

HDL Designer

Visualising RTL Design

With deep analysis capabilities, advanced creation editors, and complete project and flow management, HDL Designer delivers a powerful HDL design environment.

Precision Series

FPGA Synthesis

Provides FPGA vendor-independent logic synthesis, offering reduced time to market, fewer design defects, and superior quality of results. The powerful optimisation engines, context sensitive GUI, …

ModelSim

HDL Simulation

ModelSim’s award winning Single Kernel Simulator (SKS) technology enables transparent mixing of VHDL and Verilog in one design.

QuestaSim

Simulation and Debug

Combines high performance and capacity simulation with unified advanced debug and functional coverage for the most complete native support of Verilog, SystemVerilog, VHDL, …

Catapult HLS

High-Level Synthesis and Verification

Industry leading C++ / SystemC High-Level Synthesis with Low-Power estimation / optimization. Design checking, code, and functional coverage verification plus formal make HLS more than ….

ReqTracer

Requirements Management

Simplifies, automates, and enables requirements traceability from specification of the hardware specification through HDL coding, implementation, and validation.