HDL Designer

Overview

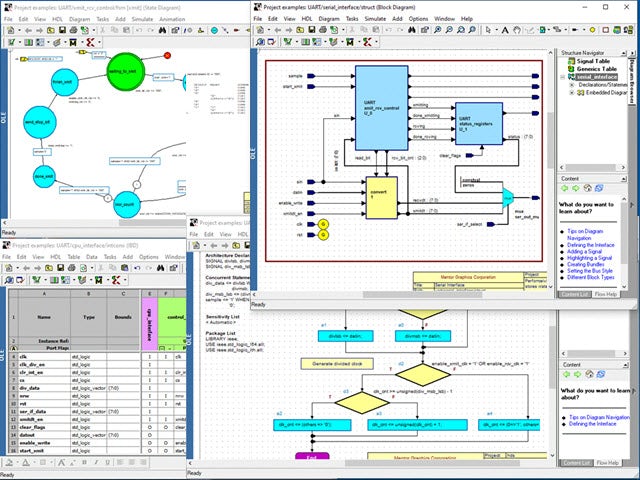

HDL Designer combines deep analysis capabilities, advanced creation editors, and complete project and flow management, to deliver a powerful HDL design environment that increases productivity of individual engineers and teams (local or remote) and enables a repeatable and predictable design process.

Whether a team is creating a design from the ground up, or evaluating RTL for reuse, HDL Designer forms a part of a complete design solution for FPGA and ASIC development. Helping engineering teams analyse, create and manage their complex designs.

Introducing HDL Designer

By using HDL Designer, savings and cost avoidance can be recognised immediately through automation and this will continue with future projects through better design reuse, consistency of coding and improved documentation. For safety- and mission-critical projects, HDL Designer’s design checking, version management, register generation and documentation support adherence to regulatory compliance mandates such as DO-254 and ISO 26262.

Accelerating RTL Reuse

Industry studies show that up to 80% of new ASIC/FPGA designs reuse code from a previous design. HDL Designer was developed to aid engineering teams in making the critical decision: to reuse or not to reuse. If the decision is to reuse code, then the design environment can quickly identify any problematic areas as well as aid engineers in understanding and adapting the code to their specific application.

Create Designs Optimally

Designing and creating large designs from IP efficiently requires more than just writing RTL. HDL Designer Series provides engineers with a suite of advanced design editors to facilitate development: interface-based design spreadsheets and state-machine editing. It also includes simulation animation within the graphical editors to maximise the benefit of the integrated flow with ModelSim, Precision Synthesis and Leonardo Spectrum.

Analyse Designs Efficiently

Hand-in-hand with code creation is code analysis. HDL Designer assists engineers in analysing complex RTL designs, providing code integrity analysis, connectivity completeness analysis, HDL code quality assessments, and design visualisation.

Design Flow Management

In conjunction with design creation and analysis, design management is the third important task facing designers. Along with managing the design data, teams need to manage the project throughout the design flow. HDL Designer tackles the design management problem by providing the designer with interfaces to other design tools within the flow; data and version management solutions.

Interested in HDL Designer?

Contact us to Learn More

Tools for FPGA & ASIC Design

HDL Designer

Visualising RTL Design

With deep analysis capabilities, advanced creation editors, and complete project and flow management, HDL Designer delivers a powerful HDL design environment.

Precision Series

FPGA Synthesis

Provides FPGA vendor-independent logic synthesis, offering reduced time to market, fewer design defects, and superior quality of results. The powerful optimisation engines, context sensitive GUI, …

ModelSim

HDL Simulation

ModelSim’s award winning Single Kernel Simulator (SKS) technology enables transparent mixing of VHDL and Verilog in one design.

QuestaSim

Simulation and Debug

Combines high performance and capacity simulation with unified advanced debug and functional coverage for the most complete native support of Verilog, SystemVerilog, VHDL, …

Catapult HLS

High-Level Synthesis and Verification

Industry leading C++ / SystemC High-Level Synthesis with Low-Power estimation / optimization. Design checking, code, and functional coverage verification plus formal make HLS more than ….

ReqTracer

Requirements Management

Simplifies, automates, and enables requirements traceability from specification of the hardware specification through HDL coding, implementation, and validation.