Catapult High-Level Synthesis & Verification

Overview

Industry leading C++ / SystemC High-Level Synthesis with Low-Power estimation / optimization. Design checking, code, and functional coverage verification plus formal make HLS more than mere “C-to-RTL”.

The broadest portfolio of hardware design solutions for C++ and SystemC based High-Level Synthesis (HLS). Catapult’s physically-aware, multi-VT mode, with Low-Power estimation and optimization, plus a range of leading Verification solutions make it more than just “C to RTL”. Catapult High-Level Synthesis & High-Level Verification (HLV) changes the game.

Introducing the Catapult High-Level Synthesis Platform

RTL productivity, especially for new and complex value-add blocks, has stalled. The design and verification challenges of creating new and novel architectures that deliver advantages in silicon for wireless, 5G, ML, or video / image processing isn’t making life any easier for design teams.

The Catapult High-Level Synthesis platform empowers designers to use industry-standard C++ and / or SystemC to describe functional intent, enabling them to move up to a more productive abstraction level for both design and verification of ASICs and FPGAs.

Architecture Exploration

Will your hardware be system performance limited? Did you pick the right fundamental memory architecture? Or did you only find out during system integration and test that real-world performance isn’t what you needed?

Are You Still Debugging RTL?

Discovering bugs late in RTL means missed opportunities, less competitive silicon, tape out delays and ECO headaches. HLS design and verification delivers right-first-time RTL designs, with reduced server and tool cost.

Optimal Power, Performance and Area

Delivering an optimal balance of Performance, Power and Area for your design needs is hard. Too little performance, too much power or too much area and you might miss a product cycle. Leverage HLS to design better and faster.

Catapult High-Level Synthesis Solutions

Catapult Synthesis solutions from Siemens deliver C++ and SystemC language support, FPGA and ASIC independence, ASIC power estimation and optimization plus the latest in physically aware multi-VT area and performance optimization.

C++ / SystemC Synthesis

A comprehensive HLS tool that covers all your needs for the most complex ASIC and FPGA designs.

Low-Power Solutions

When it comes to early architecture power estimation, plus optimizing for low-power ASIC RTL, Catapult has what you need.

Physically Aware HLS

As geometries shrink, Catapult keeps pace with design portability, physical downstream data, and exceptional QoR.

Catapult High-Level Verification Solutions

Everything you need to accelerate your High-Level Verification flow. Reduce Verification time and costs by up to 80% leveraging Design Checking, Code and Functional Coverage plus Formal.

Catapult Design Checker

Lint and formal analysis to validate your HLS designs for correctness before synthesis. Avoid design problems and QoR issues that can occur when coding for HLS.

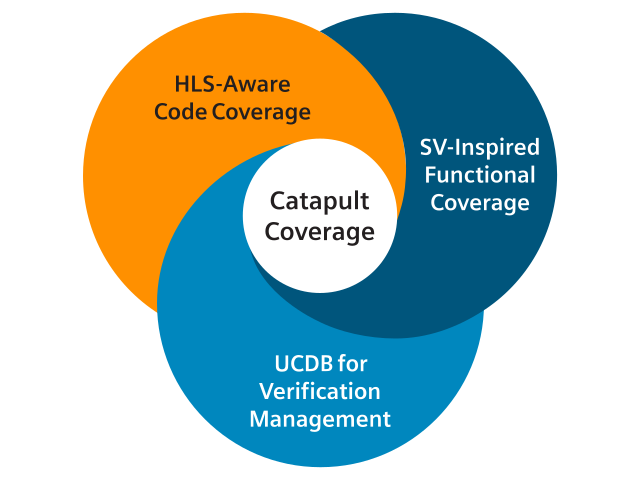

Catapult Coverage

Provides HLS-aware code coverage, including statement, branch, FEC, toggle and array access coverage. SV-inspired functional coverage with support for covergroups, coverpoints, bins and crosses.

SLEC System

Check the correctness of RTL against your High-Level models using SLEC. Enabling proof that specification and implementation are identical despite differences in language, timing, or abstraction.

Catapult Formal Verification Tools

Formally find mistakes, ambiguities and undesirable design issues, user constraints problems early in the HLS process. Even with differences in timing, and interfaces Catapult Formal enables verification and coverage closure flow.

Key Features and Benefits

- Native SystemC and ANSI C++ synthesis

- Write 80% less code for easier development and debug

- RTL optimized for power, performance, area, and RTL verification

- Simulate functionality 100-500x faster than RTL

- Production proven flows with thousands of designs

- Formally verifies designs despite language & abstraction differences

Interested in Catapult High Level Synthesis?

Contact us to Learn More

Software for IC Verification

QuestaSim

Simulation and Debug

Combines high performance and capacity simulation with unified advanced debug and functional coverage for the most complete native support of Verilog, SystemVerilog, VHDL, …

Catapult HLS

HLS and Verification

Industry leading C++ / SystemC High-Level Synthesis with Low-Power estimation / optimization. Design checking, code, and functional coverage verification plus formal make HLS more than ….

Questa Inspect

Static RTL Bug Hunting

A fully-automatic formal bug hunting app that finds deeply hidden bugs due to common RTL coding errors, Inspect makes it possible to eliminate a wide range of bugs without a testbench.

Questa CDC

CDC Verification

Questa CDC finds errors using structural analysis to detect clock-domains, synchronisers, and low power structures via the UPF. It then generates assertions and metastability models for …

Questa Lint

Static RTL Verification

Questa Lint provides adaptive, integrated insight to the designer to ensure that the quality requirements and intent are met. Pre-configured methodologies provide immediate, intuitive feedback …

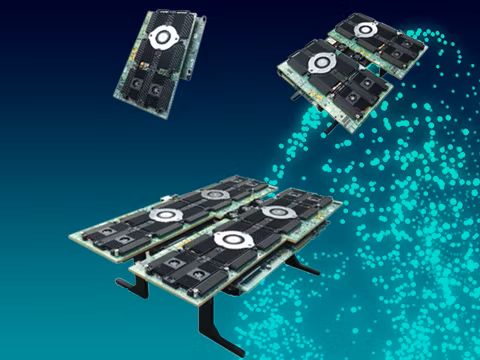

Veloce proFPGA

Hardware-Assisted Verification

The Veloce proFPGA system architecture offers best-in-class modularity, scalability, flexibility and portability to serve the verification requirements of today’s hardware and software engineers.