Questa Inspect

Overview

Find bugs early in the design! Questa Inspect automatically generates properties to support an ever-growing variety of static and dynamic checks such as dead code analysis, finite state machine deadlock, combinatorial loops, and liveness; covering common design errors and unimagined corner cases.

Automatic Code Inspection

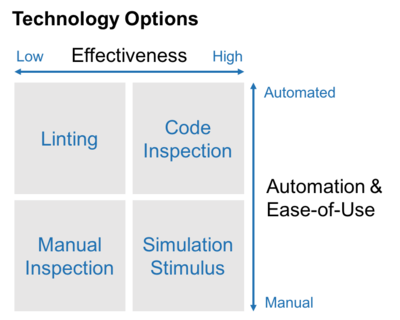

The two major methods that designers can leverage to detect bugs are static linting and simulation. Linting requires low set up and can detect a class of bugs based on the syntax of the code, although does tend to report a large number of potential issues that have to be analysed, and is limited when examining the sequential operation of a block. Simulation is focused on the code operation but requires a greater degree of set up, in the form of directed stimulus creation, which are usually not available at this stage in the process, and will only detect issues in scenarios that the provided stimulus is examining.

What designers require for early and automated detection of implementation issues are, on one hand, fast and easy to set up static checks for the sequential operation of the code in an exhaustive fashion, without relying on user provided stimulus.

Introducing Questa Inspect

SVA and PSL are time-consuming. The Questa Inspect app makes it easy to triage bugs that would otherwise require a lot of time and effort to eliminate, such as state-machine deadlock and livelock, arithmetic overflow, and out-of-range memory indexing.

Questa Inspect is an invaluable tool for designers and other engineering specialization to discover and solve problems with minimal effort. The tool replaces a substantial amount of simulation by examining code operation for known classic problems, through an exhaustive analysis of source code.

Easy-to-use

Push-button bug hunting

- No knowledge of formal or ABV is required!

- Automatic assertion creation eliminates the need to write assertions

- Leverages the common Questa Visualizer Debug Environment

Improve design quality

Finds bugs early in the design cycle

- Start verifying as soon as RTL code is written or changed

- No testbench or assertions are necessary!

- Explores sequential design behavior to find corner-case bugs that will be missed by lint

- Find common functional design issues in registers, FSMs, buses, and memories

- High signal-to-noise ratio–less likely to miss “real” issues in the noise

Automatic detection of common RTL coding errors

Finite state machine deadlock

Questa Inspect is a fully-automatic formal bug hunting app that finds bugs due to common RTL coding errors. Inspect makes it possible to eliminate a wide range of bugs with low effort. Neither a testbench nor assertions are required to be available, making it possible to start formally verifying designs as soon as the RTL code is written.

Interested in Questa Inspect?

Contact us to Learn More

Tools for Formal Verification

Questa Equivalent FPGA

FPGA Equivalence Checking

Questa Equivalent FPGA ensures advanced optimizations needed to meet aggressive power, performance & area goals do not change design functionality, ensuring errors aren’t introduced …

Questa Formal Verification

Improve Productivity and Assurance

User-friendly automated formal applications simplify the process of identifying and resolving bugs, eliminating the need for specialized formal expertise.

Questa Inspect

Static RTL Bug Hunting

A fully-automatic formal bug hunting app that finds deeply hidden bugs due to common RTL coding errors, Inspect makes it possible to eliminate a wide range of bugs without a testbench.