ModelSim

Overview

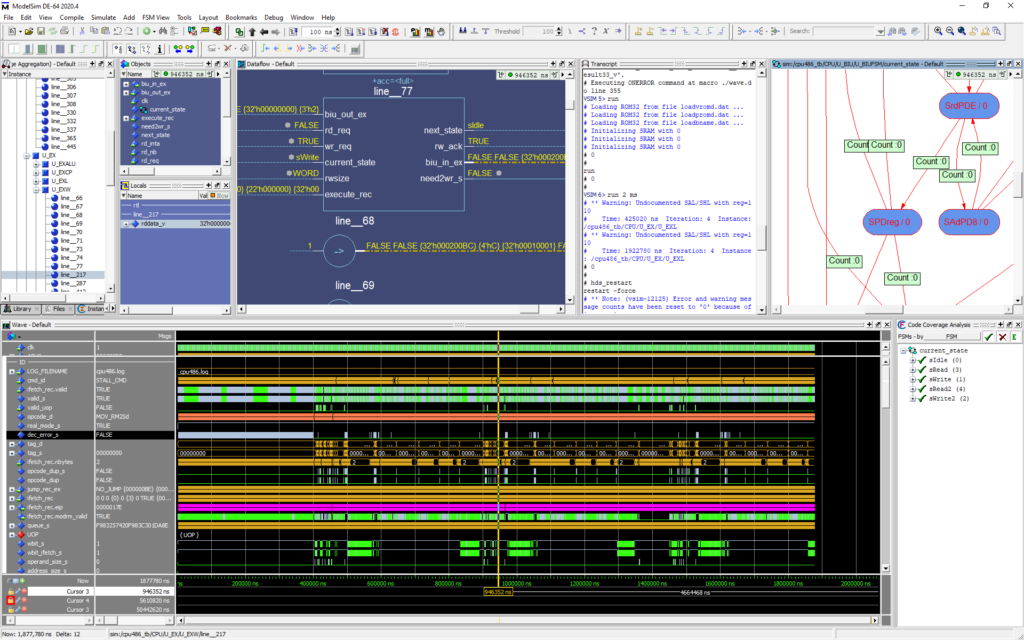

ModelSim simulates behavioral, RTL, and gate-level code – delivering increased design quality and debug productivity with platform-independent compile. Single Kernel Simulator technology enables transparent mixing of VHDL and Verilog in one design.

ModelSim packs an unprecedented level of verification capabilities into a cost-effective HDL simulator and is ideally suited for the verification of small and medium-sized FPGA designs – especially designs with complex, mission-critical functionality.

Introducing ModelSim

Many FPGA designers go to the lab before adequately vetting their design. This means weeks or even months of inefficient debugging time in the lab. With simulation the debug loop is much faster and there is complete visibility into the signals in the design. Simulation enables a higher quality FPGA design before entering the lab, allowing time spent in the lab to be more productive and focused.

ModelSim’s award-winning Single Kernel Simulator (SKS) technology enables transparent mixing of VHDL and Verilog in one design. Its architecture allows platform-independent compile with the outstanding performance of native compiled code. The debug environment efficiently displays design data for analysis and debug of all languages. ModelSim allows many debug and analysis capabilities to be employed post-simulation on saved results, as well as during live simulation runs.

Advanced Code Coverage

ModelSim’s advanced code coverage capabilities provide valuable metrics for systematic verification. Plus, ModelSim’s ease of use lowers the barriers for leveraging verification resources. All coverage information is stored in the highly efficient UCDB database. Coverage results can be viewed interactively, post-simulation, or after a merge of multiple simulation runs.

Mixed HDL Simulation

Comprehensive support of VHDL, Verilog, SystemVerilog for Design, and SystemC provide a solid foundation for single and multi-language design verification environments. An easy-to-use and unified environment provides FPGA designers the advanced capabilities they need for debugging and simulation.

Intuitive Debug Environment

ModelSim eases the process of finding design defects with an intelligently engineered debug environment that efficiently displays design data for analysis and debug of all hardware description languages. A broad set of intuitive capabilities for VHDL, Verilog, and SystemC make it the ideal choice for ASIC and FPGA design.

Key Features and Benefits

- Unified mixed language simulation engine for ease of use and performance

- Native support of VHDL, Verilog, SystemVerilog (design), SVA, PSL, and SystemC for effective verification of sophisticated design environments

- Fast time-to-debug, easy to use, multi-language debug environment

- Advanced code coverage and analysis tools for fast time to coverage closure

- Interactive and Post-Sim Debug available so same debug environment used for both

- Powerful Waveform compare for easy analysis of differences and bugs

- Unified Coverage Database with complete interactive and HTML reporting and processing, for understanding and debugging coverage throughout your project

- Coupled with HDL Designer Series for complete design creation, project management, and visualisation capabilities

- Assertions:

- Gain insight and visibility into your design by letting assertions notify you of an error so it can be fixed

- ModelSim provides a powerful library of checkers (OVL) letting you debug with assertions right away, without writing your own

- Assertions can also serve as documentation for your design, as comments are embedded into the code as you go

Interested in ModelSim?

Contact us to Learn More

Want to know about Advanced Verification?

ModelSim shares a common front end and user interface with Siemens flagship simulator Questa. This allows customers to easily upgrade for higher performance and support for Advanced Verification capabilities.

Tools for Simulation & Verification

QuestaSim

Simulation and Debug

Combines high performance and capacity simulation with unified advanced debug and functional coverage for the most complete native support of Verilog, SystemVerilog, VHDL, …

Questa Verification IP

Verification IP

Questa Verification IP (QVIP) improves quality and reduces schedule times by building protocol and methodology reusable components that support many industry standard interfaces.

ModelSim

HDL Simulation

ModelSim’s award winning Single Kernel Simulator (SKS) technology enables transparent mixing of VHDL and Verilog in one design.