IC Verification

IC verification can account for up to seventy percent of the IC design cycle. Leading verification teams not only have to ensure their designs are functionally correct, they must also validate and test their ICs in the context of the entire end-system.

Advanced Verification

Large, complex System-on-Chips (SoCs) require boosting verification productivity and managing resources more efficiently. Delivering product quality within tight schedules requires maximising verification effectiveness to speed time to coverage closure, hit quality goals and improve debug productivity.

The inclusion of multiple embedded processors and advanced interconnect systems, increasing software content, more functionality, and the configurability required by multi-platform based designs all require a functional verification solution that unifies a broad arsenal of verification solutions.

The Questa verification solution transforms verification, dramatically increasing verification productivity and managing resources more efficiently. Built on several powerful technologies, Questa continues to evolve in response to the growing complexity of SoC designs.

Questa

The Questa verification solution is an assemblage of technologies, methodologies, and libraries for modern ASIC and FPGA designs. Questa continues to evolve in response to the growing complexity of SoC designs.

DEBUG & FUNCTIONAL COVERAGE

Debug is one of the most important verification technologies and is critical for achieving productivity in today’s complex designs. Companies need debug tools that provide maximum performance, capacity and automation for the complete system-on-chip design and verification cycle.

More complex designs that include more software create new requirements for block-to-system verification reuse and the need for system verification and debug. To avoid wasting cycles at the system level, it is critical to identify bugs as early as possible and improve debug productivity.

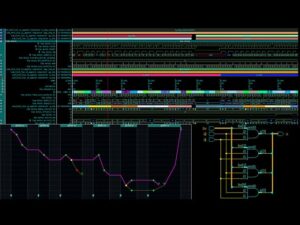

Questa Visualizer

Visualizer is a high-performance, high-capacity context aware debugger that supports a complete logic verification flow, including simulation, emulation, and prototyping.

FORMAL VERIFICATION

Designers of today’s electronics can’t afford to overlook the integrity of their design in any or all aspects including correctness, safety, trust, and security. Companies have an obligation to meet functionality, safety, and security requirements or they are met with swift ramifications. Once that occurs, consumer trust is eroded and difficult to get back. Turning out a product that has unknown performance or power issues, for example, can spell doom when detected in the field.

Meeting these requirements becomes tougher and tougher as innovation progresses, however. This up-shift means that companies have to be hyper-diligent not only about the functional correctness of their designs but also the safety, trust, and security. The design must operate as intended in even the most adverse environmental conditions and be immune to any unwarranted interference. To say it concisely, companies must be fully invested in the entire integrity of their IC – functional correctness, safety, trust, and security.

Questa Formal Verification

User-friendly automated formal applications simplify the process of identifying and resolving bugs, eliminating the need for specialized formal expertise.

FPGA PROTOTYPING

A significant evolution is underway in SoC verification, especially in the areas of AI, 5G and Automotive. Design complexity has created the need for extensive internal visibility into the design to understand subtle problems that can occur during silicon bring-up. FPGA based prototyping has become an essential tool in today’s SoC and ASIC design and verification.

The Veloce hardware-assisted verification system is the first complete, integrated offering that combines best-in-class virtual platform, hardware emulation, and FPGA prototyping technologies and paves the way to leverage the latest powerful hardware-assisted verification methodologies.

Veloce proFPGA dramatically lowers the adoption barrier of the FPGA desktop prototype solution. Together with the performance that is possible to reach thanks to its architecture innovations, the solution is easy to deploy and engineers can now bring-up on their own lab environment quickly and reliably.

Veloce proFPGA

The Veloce proFPGA system architecture offers best-in-class modularity, scalability, flexibility and portability to serve the verification requirements of today’s hardware and software engineers.

PHYSICAL VERIFICATION

New process technologies, combined with new and expanded design functionality, add up to an ever-increasing pressure for increased automation of verification and design optimisation within a set of foundry-qualified tools, all while maintaining the highest accuracy without driving up runtimes. Whether their products are custom analog, digital, mixed-signal, or system-on-chip (SoC) designs, companies need EDA tools that can deliver trusted results and help them meet their market goals.

Tight collaboration with foundries, IC design houses, and industry standards organisations ensures Calibre tools continuously provide innovative functionality that meets or exceeds state-of-the-art requirements and delivers real competitive value.

Calibre Design Solutions

Calibre Design Solutions delivers a complete IC verification and DFM optimisation platform that speeds designs from creation to manufacturing, addressing all sign-off requirements.

Software for IC Verification

QuestaSim

Simulation and Debug

Combines high performance and capacity simulation with unified advanced debug and functional coverage for the most complete native support of Verilog, SystemVerilog, VHDL, …

Catapult HLS

HLS & Verification

Industry leading C++ / SystemC High-Level Synthesis with Low-Power estimation / optimization. Design checking, code, and functional coverage verification plus formal make HLS more than ….

Questa Inspect

Static RTL Bug Hunting

A fully-automatic formal bug hunting app that finds deeply hidden bugs due to common RTL coding errors, Inspect makes it possible to eliminate a wide range of bugs without a testbench.

Questa CDC

CDC Verification

Questa CDC finds errors using structural analysis to detect clock-domains, synchronisers, and low power structures via the UPF. It then generates assertions and metastability models for …

Questa Lint

Static RTL Verification

Questa Lint provides adaptive, integrated insight to the designer to ensure that the quality requirements and intent are met. Pre-configured methodologies provide immediate, intuitive feedback …

Veloce proFPGA

Hardware-Assisted Verification

The Veloce proFPGA system architecture offers best-in-class modularity, scalability, flexibility and portability to serve the verification requirements of today’s hardware and software engineers.