Questa CDC Verification

Overview

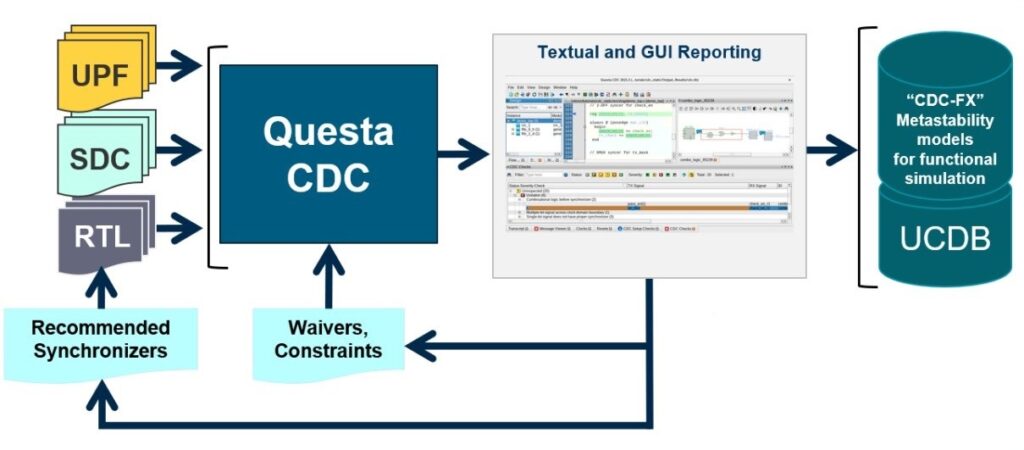

Questa CDC identifies errors using structural analysis to recognize clock-domains, synchronizers, and low power structures via the Unified Power Format (UPF). It generates assertions for protocol verification along with metastability models for reconvergence verification.

Questa CDC identifies errors to do with Clock-Domain Crossings (CDC) – signals (or groups of signals) that are generated in one clock-domain and consumed in another. It does so with structural analysis and recognition of clock-domains, synchronizers, and low power structures (via UPF); and with generation of metastability models for reconvergence verification.

Introducing Questa CDC

Designers increasingly use advanced multi-clock architectures to meet the high-performance and low-power requirements of their chips. An RTL or gate-level simulation of a design that has more than one clock domain does not accurately model the silicon behavior related to the transfer of data between asynchronous clock domains. As a consequence, simulation does not accurately predict silicon functionality, risking show-stopper bug escapes.

The technology exhaustively checks all potential CDC failures, statically verifying that all signals crossing asynchronous clock domain boundaries are guarded by CDC synchronizers. It then illustrates DUT issues found with familiar schematic and waveform displays. Additionally, in concert with Questa simulation, the CDC-FX app injects metastability into RTL functional simulation to verify the DUT is tolerant of random delays caused by metastability.

Automated assertion generation and analysis

Using only your RTL and UPF power intent file, Questa CDC solutions automatically generate and analyze assertions to rapidly identify chip-killing clock-domain crossing issues.

Industry-leading scalability and QoR

When analysing billion-gate designs, minimizing “noise” is critical. Questa CDC comprehensive, hierarchical, formal-based analysis searches through DUT elements for high throughput and noise minimization, simultaneously providing industry-leading scalability and high quality of results, while enabling CDC IP reuse.

Ease of set-up and use

Questa CDC supports the Synthesis Design Constraints (SDC) format for clock- and port- domain settings, and it includes a TCL scripting environment with powerful control and reporting capabilities. Questa CDC automatically identifies your clocks and clock distribution strategy minimizing set-up time.

Key Benefits

- Immediate productivity

- Easy set up and use

- Low noise, high accuracy

- Low power intent awareness

- Direct integration with Questa simulation

Interested in Questa CDC Verification?

Contact us to Learn More

Software for IC Verification

QuestaSim

Simulation and Debug

Combines high performance and capacity simulation with unified advanced debug and functional coverage for the most complete native support of Verilog, SystemVerilog, VHDL, …

Catapult HLS

HLS and Verification

Industry leading C++ / SystemC High-Level Synthesis with Low-Power estimation / optimization. Design checking, code, and functional coverage verification plus formal make HLS more than ….

Questa Inspect

Static RTL Bug Hunting

A fully-automatic formal bug hunting app that finds deeply hidden bugs due to common RTL coding errors, Inspect makes it possible to eliminate a wide range of bugs without a testbench.

Questa CDC

CDC Verification

Questa CDC finds errors using structural analysis to detect clock-domains, synchronisers, and low power structures via the UPF. It then generates assertions and metastability models for …

Questa Lint

Static RTL Verification

Questa Lint provides adaptive, integrated insight to the designer to ensure that the quality requirements and intent are met. Pre-configured methodologies provide immediate, intuitive feedback …

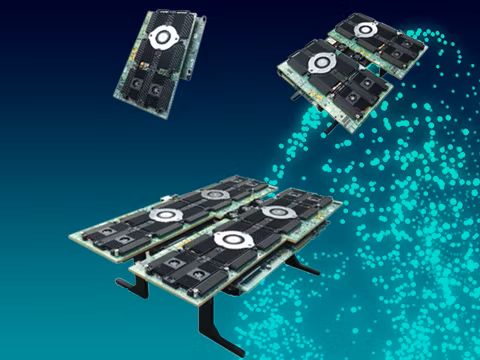

Veloce proFPGA

Hardware-Assisted Verification

The Veloce proFPGA system architecture offers best-in-class modularity, scalability, flexibility and portability to serve the verification requirements of today’s hardware and software engineers.