Questa Equivalent FPGA

Overview

Questa Equivalent FPGA (formerly known as 360 EC-FPGA) ensures advanced optimizations needed to meet aggressive power, performance & area goals do not change design functionality, ensuring errors are not introduced during synthesis or place & route.

Systematic design errors, introduced by automated design refinement tools, such as synthesis, can be hard to detect, and damaging if they make it into the final device. Formal Equivalence Checking (EC) has been used for ASIC design flows for many years. As FPGAs become bigger and critical system components, exhaustively verifying the functional equivalence of Register Transfer Level (RTL) code to synthesized netlists and the final placed & routed FPGA designs is mandatory.

Introducing Questa Equivalent FPGA (FKA 360 EC-FPGA)

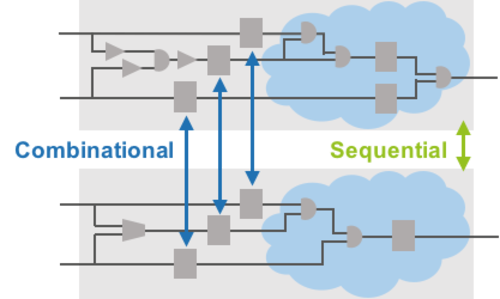

360 EC-FPGA is an automatic sequential equivalence checking tool that provides a fast and efficient method to ensure that aggressive synthesis optimizations have not introduced systematic errors that could disrupt the final design.

A major benefit of 360 EC-FPGA is to ensure that advanced FPGA synthesis optimisations, used to achieve competitive functionality, performance, power consumption, and cost targets, do not introduce functional errors. It supports all sequential synthesis optimisations performed in FPGA design flows. It verifies whole-chip, flat netlists, allowing for the most aggressive optimisations to be leveraged.

360 EC-FPGA verifies the optimised design ‘as is’ without gate-level simulation, design modifications or design restrictions, such as disabling synthesis optimisations. It eliminates the need for extensive scripting and many ‘side files’ generated by synthesis tools, providing a greater level of independence from the synthesis process.

The tool is “self-starting” by providing automated setup capabilities that detect mapping information, clocks and resets, and other initialisation settings. An advanced debugger is also included, which displays mismatches both directly in source and schematic windows, as well as through generated waveform traces.

360 EC-FPGA follows a conventional EC verification flow: design setup, mapping and comparison, and optional debug. However, the underlying sequential equivalence checking technology utilised in 360 EC-FPGA, which makes use of the OneSpin formal property checking engines, eliminates many of the design restrictions necessary with other solutions, as follows:

- Mapping: The pairing of RTL to gate flops does not need to be complete in 360 EC-FPGA to provide conclusive results

- Comparison: 360 EC-FPGA deploys sequential verification engines, generating counterexamples for some compared points independent of the mapping of other compared points

- Debug: 360 EC-FPGA utilises simulation trace based debug. Static failing patterns are generated on demand

Industry Support

Support for all major FPGA devices, including (but not limited to):

- Intel: Quartus Prime flow for the following devices: Arria and Stratix (up to 10), Cyclone and Max (up to V)

- Xilinx: Vivado flow for the following devices: Artix, Kintex, Spartan, and Virtex (up to 7 plus UltraScale/UltraScale+)

- MicroSemi: Synplify and Libero SoC flow for the following devices: Axcelerator, Fusion/SmartFusion/SmartFusion2, IGLOO/e/2/nano/PLUS, PolarFire/PolarFire SoC, ProASIC3/3E/3L/nano, ProASICPLUS, RTG4

We see the introduction of EC for FPGA to be an important addition for the validation of safety critical applications using programmable devices. As well as providing an exhaustive check, EC will identify errors quickly with the minimum of debug.

Key Features and Benefits

- Ensures that complex FPGAs are free of synthesis and optimization errors

- Dramatically accelerates the design implementation and debug loop

- Allows risk-free use of advanced synthesis optimization

- Eliminates gate level simulation and stimulus, easy to setup and apply

- Supports all FPGA synthesis optimizations, including complex sequential retiming

- Supported design languages: VHDL, Verilog, SystemVerilog, EDIF and Mixed Language

- Certified Tool Qualification Kit (TQK)

- Parallel and Distributed Operation

Interested in Questa Equivalent FPGA?

Contact us to Learn More

Tools for Formal Verification

Questa Equivalent FPGA

FPGA Equivalence Checking

Questa Equivalent FPGA ensures advanced optimizations needed to meet aggressive power, performance & area goals do not change design functionality, ensuring errors aren’t introduced …

Questa Formal Verification

Improve Productivity and Assurance

User-friendly automated formal applications simplify the process of identifying and resolving bugs, eliminating the need for specialized formal expertise.

Questa Inspect

Static RTL Bug Hunting

A fully-automatic formal bug hunting app that finds deeply hidden bugs due to common RTL coding errors, Inspect makes it possible to eliminate a wide range of bugs without a testbench.