Calibre Circuit & Reliability Verification

Overview

The Calibre Circuit Verification suite includes Layout vs Schematic (LVS), reliability verification and parasitic extraction. These tools provide sign-off quality results, as well as integration into Siemens EDA and 3rd-party products for circuit simulation and other downstream requirements.

Calibre circuit verification accurately and efficiently addresses functional yield challenges in today’s IC designs. The industry-leading Calibre nmLVS tool ensures accurate circuit behaviour with precise device parameters, while parasitic extraction tools provide the accurate and high-performance extraction required for all design styles.

Calibre reliability verification ensures designs are protected against early device failure and long-term performance degradation. A novel logic-driven layout analysis combines schematic and layout parameters for precise, accurate analysis of complex reliability concerns not possible with traditional verification tools.

Circuit & Reliability Verification

Calibre circuit verification delivers fast, efficient layout vs schematic and parasitic extraction solutions to ensure circuits will be successful when manufactured. Design verification helps ensure the robustness of a design and reduce susceptibility to premature or catastrophic electrical failures by considering the context of schematic and layout information. Designers rely on the accuracy of Calibre predictions for silicon performance and reliability to achieve first-time product success.

Calibre nmLVS

The Calibre nmLVS platform delivers high performance layout vs schematic verification, electrical rule checking, and advanced parameter calculation to validate circuit integrity and accuracy.

Calibre PERC

The Calibre PERC platform is the industry leader for reliability verification solutions, enabling a vast range of IC circuit reliability checks not possible with traditional verification tools.

Calibre xACT

The Calibre xACT tool delivers reference level accuracy for leading edge FinFET, custom, analog, and RF designs, with performance and capacity for multi-million instance digital designs.

Calibre xRC

The Calibre xRC parasitic extraction tool delivers accurate parasitic data for comprehensive and accurate post-layout analysis and simulation. Foundry-qualified for practically every process and node.

Calibre xL

The Calibre xL tool delivers fast, accurate full chip frequency dependent loop inductance and loop resistance extraction that highly correlates with field solvers and provides silicon-tested accuracy.

Interested in Calibre Design Solutions?

Contact us to Learn More

Software for IC Verification

QuestaSim

Simulation and Debug

Combines high performance and capacity simulation with unified advanced debug and functional coverage for the most complete native support of Verilog, SystemVerilog, VHDL, …

Catapult HLS

HLS and Verification

Industry leading C++ / SystemC High-Level Synthesis with Low-Power estimation / optimization. Design checking, code, and functional coverage verification plus formal make HLS more than ….

Questa Inspect

Static RTL Bug Hunting

A fully-automatic formal bug hunting app that finds deeply hidden bugs due to common RTL coding errors, Inspect makes it possible to eliminate a wide range of bugs without a testbench.

Questa CDC

CDC Verification

Questa CDC finds errors using structural analysis to detect clock-domains, synchronisers, and low power structures via the UPF. It then generates assertions and metastability models for …

Questa Lint

Static RTL Verification

Questa Lint provides adaptive, integrated insight to the designer to ensure that the quality requirements and intent are met. Pre-configured methodologies provide immediate, intuitive feedback …

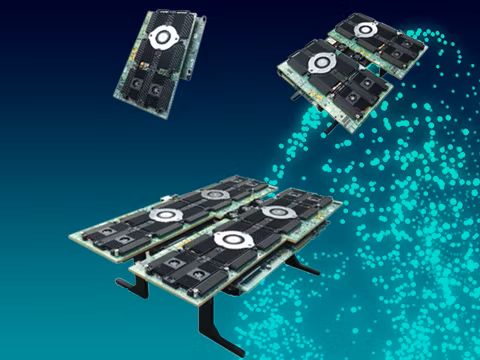

Veloce proFPGA

Hardware-Assisted Verification

The Veloce proFPGA system architecture offers best-in-class modularity, scalability, flexibility and portability to serve the verification requirements of today’s hardware and software engineers.